侧面高阻釉对压敏防雷芯片(MOV)电性能的影响

庞 驰1,费自豪2,张雷2

(1.贵州大学材料与冶金学院 贵州 贵阳550003;2.贵州飞舸电子有限公司贵州 贵阳550022 )

摘要:本文采用传统的陶瓷工艺,制备了侧面涂覆不同配方高阻釉的压敏防雷芯片,研究其对压敏防雷芯片电性能的影响。结果表明:高阻釉使芯片的均匀性得以提高、缺陷减少;提高样品的8/20 μS通流能力;在1000mA工频电流作用下,芯片的熔穿点位于芯片中部铜电极区,利于热脱离机构动作,从而提高芯片的暂态过电压耐受能力。

1. 引言

压敏防雷芯片(MOV)在使用过程中受到脉冲电压、暂态过电压、工频电压三类电应力的联合作用,消耗其能量耐量,导致性能劣化。为确保MOV品质,相关标准采用8/20 μS雷电波、2mS方波、TOV试验和加速老化寿命试验来检测MOV的各项性能。在多年的生产检测和实际使用发现:压敏防雷芯片的损坏大多数发生在芯片边缘,如8/20 μS雷电波Imax作用下,绝缘层出现打崩、闪络、边缘出现穿孔现象;2mS方波、TOV试验中芯片穿孔破坏,并且穿孔的位置绝大部分在边缘。可见芯片的边缘是压敏防雷芯片最薄弱的环节,是缺陷比较多的部分。提高压敏防雷芯片的电性能的关键是提高陶瓷基体的均匀性,减少芯片边缘的缺陷[1~3]。造成陶瓷基体不均匀的主要原因是低熔点的Bi、Sb等元素在烧结过程中的挥发,Bi、Sb等元素在芯片边缘挥发比较多,导致陶瓷基体边缘致密度下降,进而影响压敏防雷芯片的电性能。

本实验通过在侧面涂覆高阻釉,在高温烧结过程中与陶瓷基体结合为一体,补充易挥发的Bi、Sb等元素,同时Si、Sb、Y等元素渗入基体,形成浓度梯度,使边缘的压敏电压高于中心的压敏电压,从而提高压敏防雷芯片的电性能。

2. 实验

2.1 高阻釉的配制

高阻釉与陶瓷基体有很好的结合强度,其膨胀系数与基体相差不大,有一定量的玻璃质,在高温下流动时表面光洁。按表1的配方称量(质量分数),湿法球磨24h,经烘干过筛后,850℃煅烧2小时,湿法球磨10h,烘干备用。

| 编号 | ZnO | Bi2O3 | Sb2O3 | SiO2 | Y2O3 | 硼玻璃 |

| 1# | 55% | 15% | 10% | 5% | 3% | 12% |

| 2# | 50% | 15% | 15% | 7% | 3% | 10% |

| 3# | 43% | 15% | 20% | 9% | 3% | 10% |

| 4# | 36% | 15% | 25% | 11% | 3% | 10% |

2.2 样品准备

将ZnO粉料和Bi2O3、Co3O4、MnO2、Sb2O3、Cr2O3等添加剂按配方(摩尔分数):97%ZnO+1%Bi2O3+0.5%Co3O4+0.5%Sb2O3+0.5%MnO2+0.5%Cr2O3准确称量,加入适量的浓度为10%的聚乙烯醇水溶液作粘合剂,搅拌球磨5小时后喷雾造粒,干压成边长40×40mm,厚度4.4mm,密度为3.2g/cm3的生坯,缓慢升温至550℃排胶后,将前面制备的高阻釉分别加入3%酒精-乙基纤维素溶液调至一定浓度,涂覆于坯体侧面,干燥后在1150℃烧成,在650℃退火,烧渗银电极,环氧树脂包封,制得样品分别记为G0(未涂覆高阻釉)、G1(1#高阻釉)、G2(2#高阻釉)、G3(3#高阻釉)、G4(4#高阻釉)。

2.3 样品测试

用CJ1001型压敏电阻直流参数仪测量样品的压敏电压、漏电流、非线性系数,用FGL-40型雷电流冲击实验台测试8/20ms大电流特性,用FGT-TOV型老化试验台测试TOV特性,用JSM-6360LV型扫描电镜分析样品显微结构。

3. 结果与讨论

未涂覆高阻釉的G0样品与涂覆高阻釉的G1~G4样品,其压敏电压U1mA、电压梯度、流电流平均值如表1所示,从表1中可以看出:涂覆高阻釉后压敏电压、电压梯度略有升高,漏电流略有降低。

表1 涂覆不同高阻釉对小电流特性的影响

| 样品 | G0 | G1 | G2 | G3 | G4 |

| 压敏电压(V) | 618 | 625 | 630 | 635 | 636 |

| 电压梯度(V/mm) | 170 | 171 | 173 | 174 | 174 |

| 漏电流(mA) | 3.5 | 2.2 | 2.1 | 2.2 | 2.1 |

从表2中可以看出,G0样经过8/20ms雷电流30KA×15次冲击后,其压敏电压变化率为+0.3%,漏电流为6.5mA;而G3-样的压敏电压变化率为+1.6%,漏电流为2.9mA。涂覆高阻釉对8/20ms雷电流冲击后压敏电压的稳定性影响不是太大,但是对漏电流的影响较大,G3样品的性能最好。从表3可以看出,经过涂覆侧面高阻釉处理后的G2、G3、G4样品,在8/20 μS雷电波Imax作用下,芯片的绝缘性能更好,未出现击穿、闪络现象。采用环氧树脂包封的产品完全能通过行业标准,达到目前国内的最高水平。

表2涂覆不同高阻釉对8/20ms雷电流30KA的影响

| 样品 | G0 | G1 | G2 | G3 | G4 |

| 压敏电压(V) | 618 | 625 | 630 | 635 | 636 |

| 漏电流(mA) | 3.5 | 2.2 | 2.1 | 2.2 | 2.1 |

| 30KA冲击15次后 压敏电压(V) | 620 | 630 | 633 | 645 | 630 |

| 30KA冲击15次后 漏电流(mA) | 6.5 | 4.2 | 3.2 | 2.9 | 3.3 |

| 30KA冲击15次后 压敏电压变化率 | +0.3% | +0.8% | +0.5% | +1.6% | -0.9% |

表3 8/20ms雷电流30KA×15次冲击后,再冲击60KA×2次冲击

| 样品 | G0 | G1 | G2 | G3 | G4 |

| 测试结果 | 闪络 | 闪络 | 无击穿、闪络 | 无击穿、闪络 | 无击穿、闪络 |

由表4可见,涂覆侧面高阻釉后的样品与未涂覆侧面高阻釉后的样品相比,其最大的热脱扣电流有较大提高,G3样品约为1300mA。从图1中可可见,在长时间、大电流作用下,G0样品的熔穿位置位于芯片边缘,而G3样品的熔穿位置位于芯片中部铜电极区

表4 不同高阻釉对TOV特性影响

| 样品 | G0 | G1 | G2 | G3 | G4 |

| 最大热脱扣电流 | 800mA | 1000mA | 1000mA | 1300mA | 1100mA |

|  |

| 图1 G0样品在工频电流1000mA熔穿位置 | 图2 G3样品在工频电流1000mA熔穿位置 |

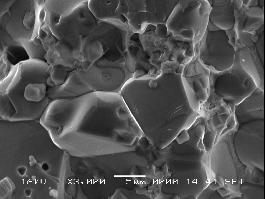

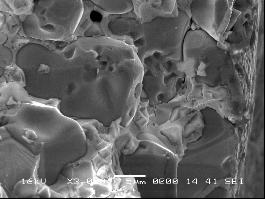

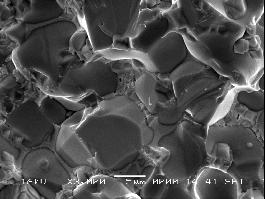

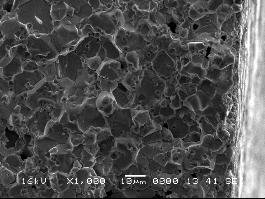

图2是G0、G3样品中心位置与边缘位置的SEM照片。从压敏陶瓷的显微结构中可以看出,在相同温度下烧成的G0、G3样品,其中心位置的晶粒尺寸约为15μm左右,G0样品边缘ZnO晶粒尺寸大于20μm,而G3样品仅仅是最外侧的ZnO晶粒尺寸大于20μm,从放大1000倍照片看出,G3样品的晶粒尺寸大致在15μm左右,其陶瓷较为致密。

|  |

| (a)G0样品中心部位 | (b)G0样品边缘部位 |

|  |

| (c)G3样品中心部位 | (d)G3样品边缘部位 |

| |

| (e)G3样品边缘部位 |

图2 不同样品的SEM照片

涂覆高阻釉后,在高温烧结过程中与陶瓷基体结合为一体,补充易挥发的Bi、Sb等元素,同时Si、Sb、Y等元素渗入基体,提高了边缘的压敏电压,在侧面形成高阻层,在8/20ms雷电流冲击作用下,脉冲电流的分布得到改善,边缘的电流密度减小,同时由于侧面高阻层的存在,提高了样品在Imax作用下抗闪络的能力。G4样品8/20ms雷电流In下的通流能力略有下降,初步分析认为:侧面涂覆更高浓度的Sb2O3、SiO2造成冲击电流向芯片中心部位集中,电流密度过大所致。对于不同的压敏防雷芯片配方体系,需要合适的高阻釉配合,达到最佳的电流分布,压敏防雷芯片的电性能才能达到最佳。

4. 结论

(1)高阻釉能提高芯片边缘的压敏电压,使芯片的均匀性得以提高、缺陷减少。

(2)8/20ms雷电流30KA冲击时,G3样品压敏电压、流电流最为稳定;8/20ms雷电流60KA冲击时,G2 、G3样品未出现击穿、闪络,侧面涂覆高阻釉能提高样品的大电流通流能力。

(3)在1000mA长时间工频电流作用下,芯片的熔穿点位于芯片中部铜电极区,击穿后的发热被铜电极吸收传导,利于热脱离机构动作,提高芯片的暂态过电压耐受能力。

参考文献

[2] 钟庆东等.氧化锌压敏电阻片侧面绝缘性能研究综述[J].上海电力学院学报,2004,6:25~28.

[3] 王茂华等.氧化锌压敏电阻器的失效模式[J].压电与声光,2005,24(9):62~64.